## 16 x 16-Bit CMOS Parallel Multiplier Accumulator

April 1997

#### Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- 16 x 16-Bit Parallel Multiplication with Accumulation to a 35-Bit Result

- · High-Speed (55ns) Multiply Accumulate Time

- Low Power CMOS Operation

- I<sub>CCSB</sub> = 500μA Maximum

- I<sub>CCOP</sub> = 7.0mA Maximum at 1.0MHz

- HMA510/883 is Compatible with the CY7C510 and the IDT7210

- Supports Two's Complement or Unsigned Magnitude Operations

- Three-State Outputs

#### Ordering Information

| PART NUMBER     | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |

|-----------------|---------------------|------------|-------------|

| HMA510GM-55/883 | -55 to 125          | 68 Ld CPGA | G68.B       |

| HMA510GM-65/883 | -55 to 125          | 68 Ld CPGA | G68.B       |

| HMA510GM-75/883 | -55 to 125          | 68 Ld CPGA | G68.B       |

#### Description

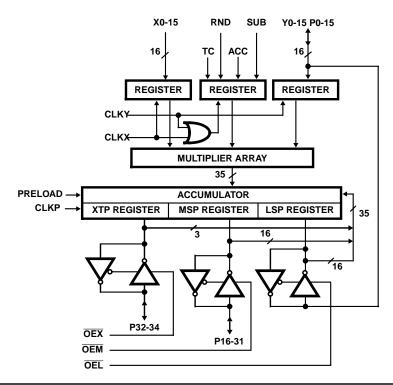

The HMA510/883 is a high speed, low power CMOS 16 x 16-bit parallel multiplier accumulator capable of operating at 55ns clocked multiply-accumulate cycles. The 16-bit X and Y operands may be specified as either two's complement or unsigned magnitude format. Additional inputs are provided for the accumulator functions which include: loading the accumulator with the current product, adding or subtracting the accumulator contents and the current product, and preloading the Accumulator Registers from the external inputs.

All inputs and outputs are registered. The registers are all positive edge triggered, and are latched on the rising edge of the associated clock signal. The 35-bit Accumulator Output Register is broken into three parts. The 16-bit least significant product (LSP), the 16-bit most significant product (MSP), and the 3-bit extended product (XTP) Registers. The XTP and MSP Registers have dedicated output ports, while the LSP Register shares the Y-inputs in a multiplexed fashion. The entire 35-bit Accumulator Output Register may be preloaded at any time through the use of the bidirectional output ports and the preloaded control.

#### **Block Diagram**

## Pinout

## **68 LEAD CPGA** TOP VIEW

| 11 |       | N/C   | X15   | RND      | ACC   | CLKY            | TC          | PREL        | CLKP        | P33 |     |  |  |

|----|-------|-------|-------|----------|-------|-----------------|-------------|-------------|-------------|-----|-----|--|--|

| 10 | X13   | X14   | OEL   | SUB      | ськх  | v <sub>cc</sub> | OEX         | OEM         | P34         | P32 | N/C |  |  |

| 9  | X11   | X12   |       |          |       |                 |             |             |             |     |     |  |  |

| 8  | Х9    | X10   |       |          |       |                 |             |             |             | P28 | P29 |  |  |

| 7  | Х7    | X8    |       |          |       |                 |             |             |             | P26 | P27 |  |  |

| 6  | Х5    | Х6    |       | TOP VIEW |       |                 |             |             |             |     | P25 |  |  |

| 5  | хз    | X4    |       |          |       |                 |             |             |             | P22 | P23 |  |  |

| 4  | X1    | X2    |       |          |       |                 |             |             |             | P20 | P21 |  |  |

| 3  | Y0/P0 | ΧO    |       |          |       |                 |             |             |             | P18 | P19 |  |  |

| 2  | N/C   | Y1/P1 | Y3/P3 | Y5/P5    | Y7/P7 | Y8/P8           | Y10/<br>P10 | Y12/<br>P12 | Y14/<br>P14 | P16 | P17 |  |  |

| 1  |       | Y2/P2 | Y4/P4 | Y6/P6    | GND   | Y9/P9           | Y11/<br>P11 | Y13/<br>P13 | Y15/<br>P15 | N/C |     |  |  |

|    | Α     | В     | С     | D        | E     | F               | G           | Н           | J           | к   | L   |  |  |

## Pin Descriptions

| NAME            | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> |      | The +5V power supply pins. 0.1μF capacitors between the V <sub>CC</sub> and GND pins are recommended.                                                                                                                                                                                                                                                                                     |

| GND             |      | The device ground.                                                                                                                                                                                                                                                                                                                                                                        |

| X0-X15          | I    | X-Input Data. These 16 data inputs provide the multiplicand which may be in two's complement or unsigned magnitude format.                                                                                                                                                                                                                                                                |

| Y0-Y15/P0-P15   | I/O  | Y-Input/LSP Output Data. This 16-bit port is used to provide the multiplier which may be in two's complement or unsigned magnitude format. It may also be used for output of the least significant product (P0-P15) or for preloading the LSP Register.                                                                                                                                   |

| P16-P3          | I/O  | MSP Output Data. This 16-bit port is used to provide the most significant product output (P16-P31). It may also be used to preload the MSP Register.                                                                                                                                                                                                                                      |

| P32-P34         | I/O  | XTP Output Data. This 3-bit port is used to provide the extended product output (P32-P34). It may also be used to preload the XTP Register.                                                                                                                                                                                                                                               |

| тс              | I    | Two's Complement Control. Input data is interpreted as two's complement when this control is HIGH. A LOW indicates the data is to be interpreted as unsigned magnitude format. This control is latched on the rising edge of CLKX or CLKY.                                                                                                                                                |

| ACC             | I    | Accumulate Control. When this control is HIGH, the Accumulator Output Register contents are added to or subtracted from the current product, and the result is stored back into the Accumulator Output Register.  When LOW, the product is loaded into the Accumulator Output Register overwriting the current contents. This control is also latched on the rising edge of CLKX or CLKY. |

## Pin Descriptions (Continued)

| NAME | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                               |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUB  | I    | Subtract Control. When both SUB and ACC are HIGH, the Accumulator Register contents are subtracted from the current product. When ACC is HIGH and SUB is LOW, the Accumulator Register contents and the current product are summed. The SUB control input is latched on the rising edge of CLKX or CLKY.                                                                  |

| RND  | I    | Round Control. When this control is HIGH, a one is added to the most significant bit of the LSP. When LOW, the product is unchanged.                                                                                                                                                                                                                                      |

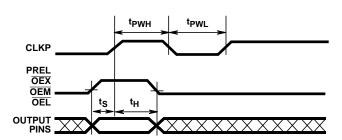

| PREL | ı    | Preload Control. When this control is HIGH, the three bidirectional ports may be used to preload the Accumulator Registers. The three-state controls ( $\overline{OEX}$ , $\overline{OEM}$ , $\overline{OEL}$ ) must be HIGH, and the data will be preloaded on the rising edge of CLKP. When this control is LOW, the Accumulator Registers function in a normal manner. |

| OEL  | ı    | Y-Input/LSP Output Port Three-State Control. When $\overline{\text{OEL}}$ is HIGH, the output drivers are in the high impedance state. This state is required for Y-data input or preloading the LSP Register. When $\overline{\text{OEL}}$ is LOW, the port is enabled for LSP output.                                                                                   |

| OEM  | I    | MSP Output Port Three-State Control. A LOW on this control line enables the port for output. When $\overline{\text{OEM}}$ is HIGH, the output drivers are in the high impedance state. This control must be HIGH for preloading the MSP Register.                                                                                                                         |

| OEX  | ı    | XTP Output Port Three-State Control. A LOW on this control line enables the port for output. When $\overline{\text{OEX}}$ is HIGH, the output drivers are in the high impedance state. This control must be HIGH for preloading the XTP Register.                                                                                                                         |

| CLKX | I    | X-Register Clock. The rising edge of this clock latches the X-Data Input Register along with the TC, ACC, SUB and RND inputs.                                                                                                                                                                                                                                             |

| CLKY | ı    | Y-Register Clock. The rising edge of this clock latches the Y-Data Input Register along with the TC, ACC, SUB and RND inputs.                                                                                                                                                                                                                                             |

| CLKP | I    | Product Register Clock. The rising edge of CLKP latches the LSP, MSP and XTP Registers. If the preload control is active, the data on the I/O ports is loaded into these registers. If preload is not active, the accumulated product is loaded into the registers.                                                                                                       |

#### **Absolute Maximum Ratings**

| Supply Voltage                  | +8.0V                        |

|---------------------------------|------------------------------|

| Input or Output Voltage Applied | G ND -0.5V to $V_{CC}$ +0.5V |

| ESD Classification              | Class 1                      |

#### **Operating Conditions**

| Voltage Range     | +4.5V to +5.5V |

|-------------------|----------------|

| Temperature Range | 55°C to 125°C  |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)   | JA (C/W)           | OC (OC/M)               |

|----------------------------------------|--------------------|-------------------------|

| CPGA Package                           | 43                 | 10                      |

| Maximum Package Power Dissipation at 1 | 125 <sup>0</sup> C |                         |

| CPGA Package                           |                    | 1.17W                   |

| Maximum Junction Temperature           |                    |                         |

| Maximum Storage Temperature Range .    | 65                 | <sup>o</sup> C to 150°C |

| Maximum Lead Temperature (Soldering 1  | 0s)                | 300°C                   |

#### **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### TABLE 1. HMA5IO/883 DC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

| PARAMETER                         | SYMBOL            | TEST CONDITIONS                                                                                       | GROUP A<br>SUBGROUPS | TEMPERATURE (°C)           | MIN | MAX | UNITS |

|-----------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|----------------------|----------------------------|-----|-----|-------|

| Logical One Input<br>Voltage      | V <sub>IH</sub>   | V <sub>CC</sub> = 5.5V                                                                                | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | 2.2 | -   | V     |

| Logical Zero Input<br>Voltage     | V <sub>IL</sub>   | V <sub>CC</sub> = 4.5V                                                                                | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.8 | V     |

| Output HIGH Voltage               | V <sub>ОН</sub>   | I <sub>OH</sub> = -400μA<br>V <sub>CC</sub> = 4.5V (Note 2)                                           | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | 2.6 | -   | V     |

| Output LOW Voltage                | V <sub>OL</sub>   | I <sub>OL</sub> = +4.0mA<br>V <sub>CC</sub> = 4.5V (Note 2)                                           | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.4 | V     |

| Input Leakage Current             | lį                | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                              | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | -10 | +10 | μΑ    |

| Output or I/O Leakage<br>Current  | Io                | $V_{OUT} = V_{CC}$ or GND,<br>$V_{CC} = 5.5V$                                                         | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | -10 | +10 | μА    |

| Standby Power Supply<br>Current   | I <sub>CCSB</sub> | $V_{IN} = V_{CC}$ or GND,<br>$V_{CC} = 5.5V$ ,<br>Outputs Open                                        | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 500 | μА    |

| Operating Power Supply<br>Current | ICCOP             | $ f = 1.0 \text{MHz}, V_{\text{IN}} = V_{\text{CC}} $ or GND $V_{\text{CC}} = 5.5 \text{V} $ (Note 3) | 1, 2, 3              | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 7.0 | mA    |

| Functional Test                   | FT                | (Note 4)                                                                                              | 7, 8                 | -55 ≤ T <sub>A</sub> ≤ 125 | -   | -   |       |

#### NOTES:

- 2. Interchanging of force and sense conditions is permitted.

- 3. Operating Supply Current a proportional to frequency, typical rating is 5mA/MHz.

- 4. Tested as follows: f = 1MHz,  $V_{IH}$  (clock inputs) = 3.2V,  $V_{IH}$  (all other inputs) = 2.6V,  $V_{IL} = 0.4V$ ,  $V_{OH} \ge 1.5V$ , and  $V_{OL} \le 1.5V$ .

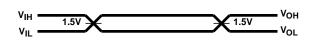

#### TABLE 2. HMA510/883 AC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

|                          |                 | (NOTE 5)   | GROUP A   |                            | -į  | 55  | -6  | 65  | -7  | 75  |       |

|--------------------------|-----------------|------------|-----------|----------------------------|-----|-----|-----|-----|-----|-----|-------|

| PARAMETER                | SYMBOL          | CONDITIONS | SUBGROUPS | TEMPERATURE (°C)           | MIN | MAX | MIN | MAX | MIN | MAX | UNITS |

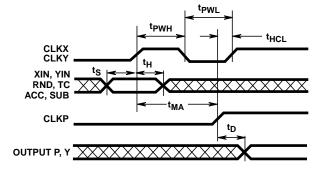

| Multiply Accumulate Time | t <sub>MA</sub> |            | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 55  | -   | 65  | -   | 75  | ns    |

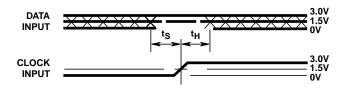

| Input Setup Time         | tS              |            | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 20  | -   | 25  | -   | 25  | -   | ns    |

#### TABLE 2. HMA510/883 AC ELECTRICAL PERFORMANCE SPECIFICATIONS (Continued)

Device Guaranteed and 100% Tested

|                            |                  | (NOTE 5)   | GROUP A   |                            |     | 55  | -6  | <b>3</b> 5 | -7  | 75  |       |

|----------------------------|------------------|------------|-----------|----------------------------|-----|-----|-----|------------|-----|-----|-------|

| PARAMETER                  | SYMBOL           | CONDITIONS | SUBGROUPS | TEMPERATURE (°C)           | MIN | MAX | MIN | MAX        | MIN | MAX | UNITS |

| Clock HIGH<br>Pulse Width  | tpWH             |            | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 20  | -   | 25  | -          | 25  | -   | ns    |

| Clock LOW<br>Pulse Width   | t <sub>PWL</sub> |            | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 20  | -   | 25  | -          | 25  | -   | ns    |

| Output Delay               | t <sub>D</sub>   |            | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 30  | -   | 35         | -   | 35  | ns    |

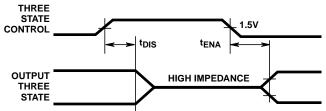

| Three-State<br>Enable Time | t <sub>ENA</sub> | (Note 5)   | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 30  | -   | 30         | -   | 35  | ns    |

#### NOTES:

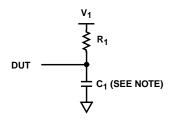

- 5. AC Testing as follows:  $V_{CC}$  = 4.5V and 5.5V. Input levels 0V and 3.0V (0V and 3.2V tor clock inputs). Timing reference levels = 1.5V, Output load per test load circuit, with  $V_1$  = 2.4V,  $R_1$  = 500 $\Omega$  and  $C_L$  = 40pF.

- 6. Transition is measured at 1200mV from steady state voltage, Output loading per test load circuit, with  $V_1 = 1.5V$ ,  $R_1 = 500\Omega$  and  $C_L = 40pF$ .

TABLE 3. HMA510/883 ELECTRICAL PERFORMANCE SPECIFICATIONS

|                          |                  | TEST                                                                                           |      |                            |     | -55 -65 |     | 65  | -75 |     |       |

|--------------------------|------------------|------------------------------------------------------------------------------------------------|------|----------------------------|-----|---------|-----|-----|-----|-----|-------|

| PARAMETER                | SYMBOL           | CONDITIONS                                                                                     | NOTE | TEMPERATURE (°C)           | MIN | MAX     | MIN | MAX | MIN | MAX | UNITS |

| Input Capacitance        | C <sub>IN</sub>  | V <sub>CC</sub> = Open,<br>f = 1MHz All mea-<br>surements are ref-<br>erenced to device<br>GND | 1    | T <sub>A</sub> = 25        | -   | 10      | 1   | 10  | 1   | 10  | pF    |

| Output Capacitance       | C <sub>OUT</sub> |                                                                                                | 1    | T <sub>A</sub> = 25        | -   | 10      | -   | 10  | -   | 10  | pF    |

| I/O Capacitance          | C <sub>I/O</sub> |                                                                                                | 1    | T <sub>A</sub> = 25        | -   | 15      | ı   | 15  | 1   | 15  | pF    |

| Input Hold Time          | t <sub>H</sub>   |                                                                                                | 1    | -55 ≤ T <sub>A</sub> ≤ 125 | 3   | -       | 3   | -   | 3   | -   | ns    |

| Three-State Disable Time | t <sub>DIS</sub> |                                                                                                | 1    | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 30      | -   | 30  | -   | 30  | ns    |

| Output Rise Time         | t <sub>r</sub>   | From 0.8V to 2.0V                                                                              | 1    | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 10      | - 1 | 10  | 1   | 10  | ns    |

| Output Fall Time         | t <sub>f</sub>   | From 2.0V to 0.8V                                                                              | 1    | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 10      | -   | 10  | -   | 10  | ns    |

#### NOTE:

**TABLE 4. APPLICABLE SUBGROUPS**

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| Initial Test       | 100%/5004    | -                             |

| Interim Test       | 100%/5004    | -                             |

| PDA                | 100%         | 1                             |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10,11           |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C and D     | Samples/5005 | 1, 7, 9                       |

<sup>7.</sup> The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes.

#### **AC Test Circuit**

## AC Testing Input, Output Waveforms

NOTE: Includes Stray and Jig Capacitance

NOTE: AC Testing: All Parameters tested as per test circuit. Input rise and fall times are driven at 1ns/V.

## **Timing Diagram**

FIGURE 1. SET-UP AND HOLD TIME

FIGURE 2. THREE-STATE CONTROL

FIGURE 3. HMA510 TIMING DIAGRAM

FIGURE 4. PRELOAD TIMING DIAGRAM

## **Burn-In Circuit**

## **68 LEAD CPGA**TOP VIEW

| 11 |       | N/C   | X15   | RND   | ACC   | CLKY            | тс          | PREL        | CLKP        | P33 |     |

|----|-------|-------|-------|-------|-------|-----------------|-------------|-------------|-------------|-----|-----|

| 10 | X13   | X14   | ŌĒĹ   | SUB   | CLKX  | V <sub>CC</sub> | ŌEX         | ŌĒM         | P34         | P32 | N/C |

| 9  | X11   | X12   | -     |       |       |                 |             |             |             | P30 | P31 |

| 8  | Х9    | X10   |       |       |       |                 |             |             |             | P28 | P29 |

| 7  | Х7    | Х8    |       |       |       |                 |             |             |             | P26 | P27 |

| 6  | Х5    | Х6    |       |       |       |                 |             |             |             | P24 | P25 |

| 5  | хз    | X4    |       |       |       |                 |             |             |             | P22 | P23 |

| 4  | X1    | X2    |       |       |       |                 |             |             |             | P20 | P21 |

| 3  | Y0/P0 | ΧO    |       |       |       |                 |             |             |             | P18 | P19 |

| 2  | N/C   | Y1/P1 | Y3/P3 | Y5/P5 | Y7/P7 | Y8/P8           | Y10/<br>P10 | Y12/<br>P12 | Y14/<br>P14 | P16 | P17 |

| 1  |       | Y2/P2 | Y4/P4 | Y6/P6 | GND   | Y9/P9           | Y11/<br>P11 | Y13/<br>P13 | Y15/<br>P15 | N/C |     |

|    | Α     | В     | С     | D     | E     | F               | G           | Н           | J           | К   | L   |

| CPGA PIN | PIN NAME | BURN-IN SIGNAL |

|----------|----------|----------------|

| B6       | X6       | F1             |

| A6       | X5       | F2             |

| B5       | X4       | F3             |

| A5       | Х3       | F4             |

| B4       | X2       | F5             |

| A4       | X1       | F6             |

| В3       | X0       | F7             |

| A3       | Y0/P0    | F8             |

| B2       | Y1/P1    | F9             |

| B1       | Y2/P2    | F10            |

| C2       | Y3/P3    | F11            |

| C1       | Y4/P4    | F12            |

| D2       | Y5/P5    | F13            |

| D1       | Y6/P6    | F14            |

| E2       | Y7/P7    | F15            |

| E1       | GND      | GND            |

| F2       | Y8/P8    | F1             |

| F1       | Y9/P9    | F2             |

| G2       | Y10/P10  | F3             |

| CPGA PIN | PIN NAME | BURN-IN SIGNAL     |

|----------|----------|--------------------|

| G1       | Y11/P11  | F5                 |

| H2       | Y12/P12  | F4                 |

| H1       | Y13/P13  | F4                 |

| J2       | Y14/P14  | F8                 |

| J1       | Y15/P15  | F9                 |

| K2       | P16      | V <sub>CC</sub> /2 |

| L2       | P17      | V <sub>CC</sub> /2 |

| K3       | P18      | V <sub>CC</sub> /2 |

| L3       | P19      | V <sub>CC</sub> /2 |

| K4       | P20      | V <sub>CC</sub> /2 |

| L4       | P21      | V <sub>CC</sub> /2 |

| K5       | P22      | V <sub>CC</sub> /2 |

| L5       | P23      | V <sub>CC</sub> /2 |

| K6       | P24      | V <sub>CC</sub> /2 |

| L6       | P25      | V <sub>CC</sub> /2 |

| K7       | P26      | V <sub>CC</sub> /2 |

| L7       | P27      | V <sub>CC</sub> /2 |

| K8       | P28      | V <sub>CC</sub> /2 |

| L8       | P29      | V <sub>CC</sub> /2 |

| CPGA PIN | PIN NAME        | BURN-IN SIGNAL     |

|----------|-----------------|--------------------|

| K9       | P30             | V <sub>CC</sub> /2 |

| L9       | P31             | V <sub>CC</sub> /2 |

| K10      | P32             | V <sub>CC</sub> /2 |

| K11      | P33             | V <sub>CC</sub> /2 |

| J10      | P34             | V <sub>CC</sub> /2 |

| J11      | CLKP            | F0                 |

| H10      | ŌĒM             | GND                |

| H11      | PREL            | F6                 |

| G10      | ŌEX             | GND                |

| G11      | TC              | F5                 |

| F10      | V <sub>CC</sub> | V <sub>CC</sub>    |

| F11      | CLKY            | F0                 |

| E10      | CLKY            | F0                 |

| E11      | ACC             | F1                 |

| D10      | SUB             | F2                 |

| D11      | RND             | F3                 |

| C10      | ŌĒĹ             | V <sub>CC</sub>    |

| C11      | X15             | F8                 |

| B10      | X14             | F9                 |

| A10      | X13             | F10                |

| B9       | X12             | F11                |

| A9       | X11             | F12                |

| B8       | X10             | F13                |

| A8       | X9              | F14                |

| B7       | X8              | F15                |

| A7       | X7              | F7                 |

| A2       | N.C.            | N.C.               |

| K1       | N.C.            | N.C.               |

| L10      | N.C.            | N.C.               |

| B11      | N.C.            | N.C.               |

#### NOTES:

- 8.  $V_{CC}$  = 5.5V +0.5V/-0.0V with 0.1µF decoupling capacitor to GND.

- 10.  $V_{IH} = V_{CC}$  1V  $\pm 0.5 V$  (Min),  $V_{IL} = 0.8 V$  (Max).

- 11. 47k $\Omega$  load resistors used on all pins except V  $_{CC}$  and GND (Pin-Grid identifiers F10, G10, G11 and H11).

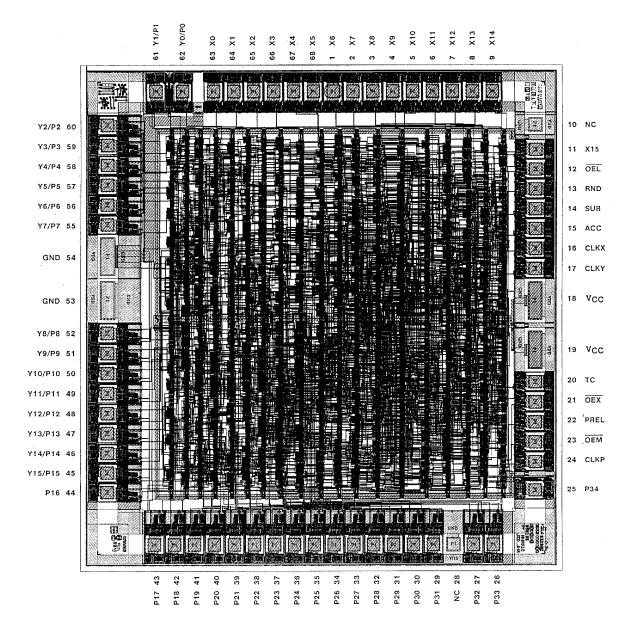

#### Die Characteristics

**DIE DIMENSIONS:**

$184 \times 176 \times 19 \pm 1 \text{mils}$

**METALLIZATION:**

Type: Si - Al or Si-Al-Cu

Thickness: 8kÅ

#### **GLASSIVATION:**

Type: Nitrox Thickness: 10kÅ

WORST CASE CURRENT DENSITY: 0.9 x 10<sup>5</sup>A/cm<sup>2</sup>

### Metallization Mask Layout

#### HMA510/883

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com