# **MOS Integrated Circuit**

# $\mu$ PD78P322

### 16/8-BIT SINGLE-CHIP MICROCONTROLLER

The  $\mu$ PD78P322 is a version provided by replacing the  $\mu$ PD75322's internal mask ROM with one-time PROM or EPROM.

Because the one-time PROM version is programmable only once by users, it is ideally suited for small-scale production of many different products, and rapid development and time-to-market of application sets.

The EPROM version is reprogrammable, and suited for the evaluation of systems.

The  $\mu$ PD78P322K, which is the EPROM version, does not maintain planned reliability when used in mass-produced products. Please use only experimentally or for evaluating functions during trial manufacture.

Functions are described in detail in the following user's manual. Be sure to read it for designing.  $\mu$ PD78322 User's Manual: IEU-1248

#### **FEATURES**

- μPD78322 compatible

- ullet For mass-production, the  $\mu$ PD78P322 can be replaced with the  $\mu$ PD78322 which incorporates mask ROM

- Internal PROM: 16,384 × 8 bits

- Programmable once only (one-time PROM version without window)

- Erasable with ultraviolet rays and electrically programmable (EPROM version with window)

- PROM programming characteristics: μPD27C256A compatible

- The μPD78P328 is a QTOP<sup>™</sup> microcontroller

**Remark** QTOP microcontroller is a general term for microcontrollers which incorporate one-time PROM, and are totally supported by NEC's programming service (from programming to marking, screening, and verification).

#### ORDERING INFORMATION

| Part Number |                      | Package                                   | Internal ROM  | Quality Grade  |

|-------------|----------------------|-------------------------------------------|---------------|----------------|

|             | μPD78P322GF-3B9      | 80-pin plastic QFP (14 × 20 mm)           | One-time PROM | Standard       |

|             | $\mu$ PD78P322GJ-5BJ | 74-pin plastic QFP (20 $\times$ 20 mm)    | One-time PROM | Standard       |

|             | $\mu$ PD78P322L      | 68-pin plastic QFJ (950 $	imes$ 950 mils) | One-time PROM | Standard       |

|             | $\mu$ PD78P322K      | 80-pin ceramic WQFN                       | EPROM         | Not applicable |

|             | $\mu$ PD78P322KC     | 68-pin ceramic WQFN                       | EPROM         | Standard       |

|             | $\mu$ PD78P322KD     | 74-pin ceramic WQFN                       | EPROM         | Standard       |

|             |                      |                                           |               |                |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

Functions common to the one-time PROM and EPROM versions are referred to as PROM functions throughout this document.

The information in this document is subject to change without notice.

Document No. U10435EJ5V0DS00 (5th edition) (Previous No. IC-2485)

Date Published Printed in Japan

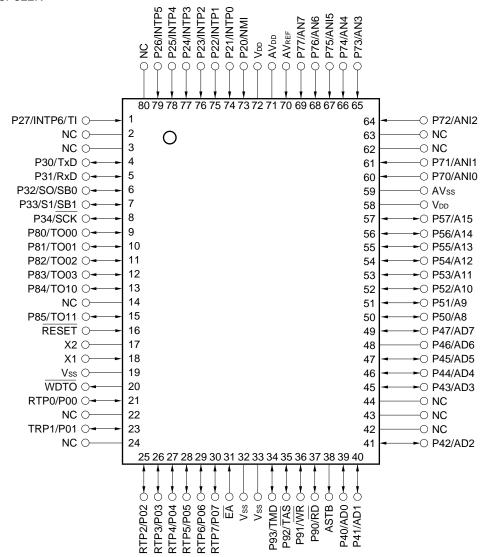

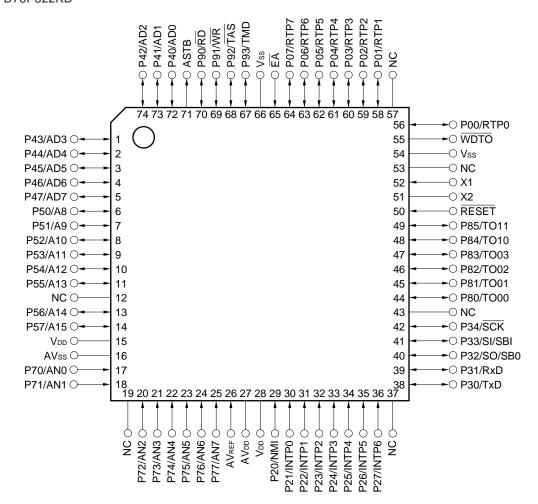

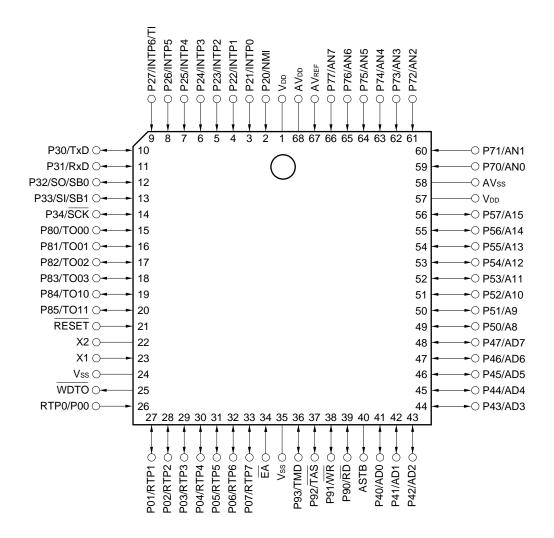

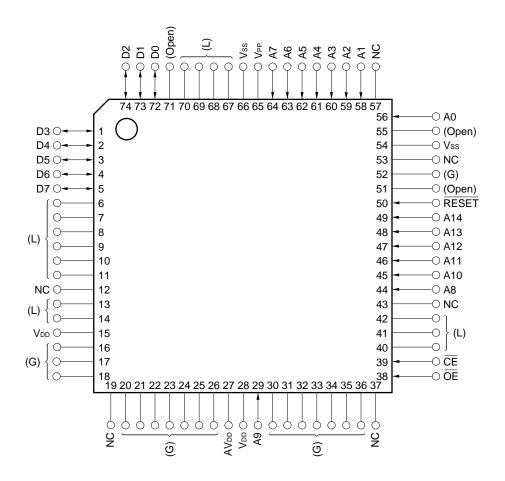

#### PIN CONFIGURATIONS (Top View)

- (1) Normal operating mode

- 80-pin plastic QFP (14  $\times$  20 mm)  $\mu$ PD78P322GF-3B9

- 80-pin ceramic WQFN μPD78P322K

Caution Connect NC pins to Vss as a measure against noise (can leave open).

**Remark** These pins are compatible with the  $\mu$ PD78322GF pins.

The  $\mu$ PD78P322K does not maintain planned reliability when used in mass-produced products. Please use only experimentally or for evaluating functions during trial manufacture.

- 74-pin plastic QFP (20  $\times$  20 mm)  $\mu$ PD78P322GJ-5BJ

- 74-pin ceramic WQFN μPD78P322KD

Caution Connect NC pins to Vss for measures against noise (can leave open).

**Remark** These pins are compatible with the  $\mu$ PD78322GJ pins.

- 68-pin plastic QFJ (950  $\times$  950 mils)  $\mu$ PD78P322L

- 68-pin ceramic WQFN μPD78P322KC

**Remark** These pins are compatible with the  $\mu$ PD78322L pins.

| P00-P07     | : Port 0                     | RESET     | : Reset                    |

|-------------|------------------------------|-----------|----------------------------|

| P20-P27     | : Port 2                     | X1, X2    | : Crystal                  |

| P30-P34     | : Port 3                     | WDTO      | : Watchdog Timer Output    |

| P40-P47     | : Port 4                     | ĒΑ        | : External Access          |

| P50-P57     | : Port 5                     | TMD       | : Turbo Mode               |

| P70-P77     | : Port 7                     | TAS       | : Turbo Access Strobe      |

| P80-P85     | : Port 8                     | WR        | : Write Strobe             |

| P90-P93     | : Port 9                     | RD        | : Read Strobe              |

| NMI         | : Nonmaskable Interrupt      | ASTB      | : Address Strobe           |

| INTP0-INTP6 | : Interrupt From Peripherals | AD0-AD7   | : Address/Data Bus         |

| RTP0-RTP7   | : Real-Time Port             | A8-A15    | : Address Bus              |

| TI          | : Timer Input                | AN0-AN7   | : Analog Input             |

| TxD         | : Transmit Data              | AVREF     | : Analog Reference Voltage |

| RxD         | : Receive Data               | AVss      | : Analog Vss               |

| SB0/SO      | : Serial Bus/Serial Output   | $AV_{DD}$ | : Analog V <sub>DD</sub>   |

| SB1/SI      | : Serial Bus/Serial Input    | $V_{DD}$  | : Power Supply             |

| SCK         | : Serial Clock               | Vss       | : Ground                   |

| TO00-TO03   | :1                           | NC        | : No Connection            |

| TO10, TO11  | : } Timer Output             |           |                            |

|             |                              |           |                            |

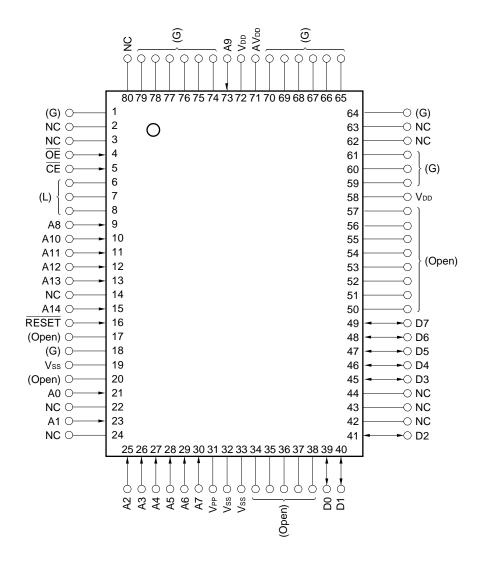

- (2) PROM programming mode ( $\overline{RESET} = H$ , AVDD = L)

- $\bullet$  80-pin plastic QFP (14  $\times$  20 mm)

μPD78P322GF-3B9

• 80-pin ceramic WQFN  $\mu$ PD78P322K

Cautions 1. The recommended connection of the unused pins in the PROM programming mode are indicated in parentheses.

L : Connect each pin to Vss via a resistor.

G : Connect the pin to Vss.

Open : Leave the pin unconnected.

2. Connect NC pins to Vss for measures against noise (can leave open).

The  $\mu$ PD78P322K does not maintain planned reliability when used in mass-produced products. Please use only experimentally or for evaluating functions during trial manufacture.

• 74-pin plastic QFP (20  $\times$  20 mm)  $\mu$ PD78P322GJ-5BJ

• 74-pin ceramic WQFN μPD78P322KD

Cautions 1. The recommended connection of the unused pins in the PROM programming mode are indicated in parentheses.

E : Connect each pin to Vss via a resistor.

G : Connect the pin to Vss.

Open : Leave the pin unconnected.

2. Connect NC pins to Vss as measure against noise.

- 68-pin plastic QFJ (950  $\times$  950 mil)  $\mu$ PD78P322L

- 68-pin ceramic WQFN μPD78P322KC

Caution The recommended connection of the unused pins in the PROM programming mode are indicated in parentheses.

L : Connect each pin to Vss via a resistor.

G : Connect the pin to Vss.

Open : Leave the pin unconnected.

CE : Chip Enable VPP : Programming Power Supply

OE : Output Enable NC : No Connection

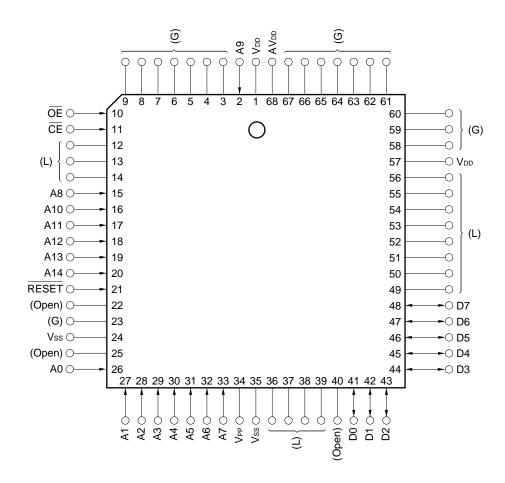

**BLOCK DIAGRAM**

# **CONTENTS**

| 1. | PIN FUNCTIONS 11                                                           |  |  |  |  |

|----|----------------------------------------------------------------------------|--|--|--|--|

|    | 1.1 Normal Operating Mode 11                                               |  |  |  |  |

|    | 1.2 PROM Programming Mode (RESET = H, AVDD = L) 13                         |  |  |  |  |

|    | 1.3 Pin Input/Output Circuits and Recommended Connection of Unused Pins 14 |  |  |  |  |

| 2. | DIFFERENCES BETWEEN $\mu$ PD78P322 and $\mu$ PD78322 16                    |  |  |  |  |

| 3. | PROM PROGRAMMING 17                                                        |  |  |  |  |

|    | 3.1 Operation Mode 17                                                      |  |  |  |  |

|    | 3.2 PROM Write Procedure 18                                                |  |  |  |  |

|    | 3.3 PROM Read Procedure 20                                                 |  |  |  |  |

| 4. | ERASURE CHARACTERISTICS (FOR $\mu$ PD78P322K/KC/KD ONLY) 21                |  |  |  |  |

| 5. | OPAQUE FILM ON ERASURE WINDOW (FOR $\mu$ PD78P322K/KC/KD ONLY) 21          |  |  |  |  |

| 6. | ONE-TIME PROM VERSION SCREENING 21                                         |  |  |  |  |

| 7. | ELECTRICAL SPECIFICATIONS 22                                               |  |  |  |  |

| 8. | PACKAGE DRAWINGS 36                                                        |  |  |  |  |

| 9. | RECOMMENDED SOLDERING CONDITIONS 42                                        |  |  |  |  |

| AP | PPENDIX A. DRAWINGS OF CONVERSION SOCKETS AND RECOMMENDED FOOTPRINTS 44    |  |  |  |  |

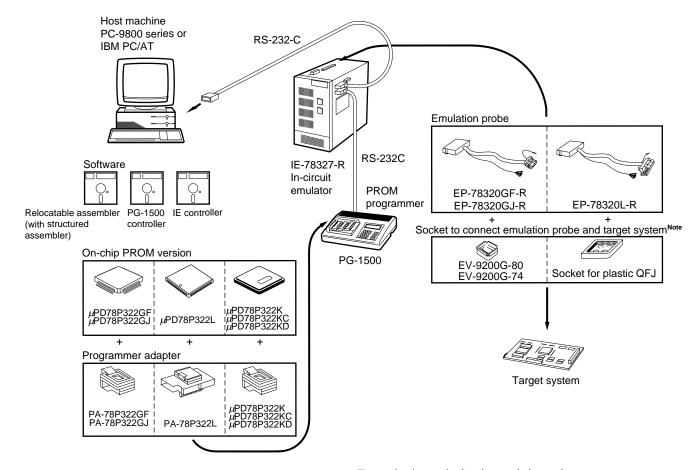

| AP | PPENDIX B. TOOLS 48                                                        |  |  |  |  |

|    | B.1 Development Tools 48                                                   |  |  |  |  |

|    | B.2 Evaluation Tools 52                                                    |  |  |  |  |

\*

B.3 Embedded Software ... 52

# 1. PIN FUNCTIONS

# 1.1 Normal Operating Mode

# (1) Port Pins

| Pin Name | Input/Output | Function                                              | Alternate |

|----------|--------------|-------------------------------------------------------|-----------|

|          |              |                                                       | Function  |

| P00-P07  | Input/Output | PORT0                                                 | RTP0-RTP7 |

|          | (Output)     | 8-bit input/output port                               |           |

|          |              | Input or output mode can be specified bit-wise.       |           |

|          |              | The port can also operate as a real-time output port. |           |

| P20      | Input        | PORT 2                                                | NMI       |

| P21      |              | 8-bit input-only port                                 | INTP0     |

| P22      |              |                                                       | INTP1     |

| P23      |              |                                                       | INTP2     |

| P24      |              |                                                       | INTP3     |

| P25      |              |                                                       | INTP4     |

| P26      |              |                                                       | INTP5     |

| P27      |              |                                                       | INTP6/TI  |

| P30      | Input/Output | PORT 3                                                | TxD       |

| P31      |              | 5-bit input/output port                               | RxD       |

| P32      |              | Input or output mode can be specified bit-wise.       | SO/SB0    |

| P33      |              |                                                       | SI/SB1    |

| P34      |              |                                                       | SCK       |

| P40-P47  | Input/Output | PORT 4                                                | AD0-AD7   |

|          |              | 8-bit input/output port                               |           |

|          |              | Input or output mode can be specified in 8-bit units. |           |

| P50-P57  | Input/Output | PORT 5                                                | A8-A15    |

|          |              | 8-bit input/output port                               |           |

|          |              | Input or output mode can be specified bit-wise.       |           |

| P70-P77  | Input        | PORT 7                                                | AN0-AN7   |

|          |              | 8-bit input-only port                                 |           |

| P80      | Input/Output | PORT 8                                                | TO00      |

| P81      |              | 6-bit input/output port                               | TO01      |

| P82      |              | Input or output mode can be specified bit-wise.       | TO02      |

| P83      |              |                                                       | TO03      |

| P84      |              |                                                       | TO10      |

| P85      |              |                                                       | TO11      |

| P90      | Input/Output | PORT 9                                                | RD        |

| P91      |              | 4-bit input/output port                               | WR        |

| P92      |              | Input or output mode can be specified bit-wise.       | TAS       |

| P93      |              |                                                       | TMD       |

# (2) Non-Port Pins (1/2)

| Pin Name  | Input/Output | Function                                                                                                                | Alternate |

|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------|-----------|

|           |              |                                                                                                                         | Function  |

| RTP0-RTP7 | Output       | Real-time output port which outputs a pulse in synchronization with the trigger signal from                             | P00-P07   |

|           |              | the real-time pulse unit (RPU).                                                                                         |           |

| INTP0     | Input        | Edge-detected external interrupt request input.                                                                         | P21       |

| INTP1     |              | The valid edge can be specified in the mode register.                                                                   | P22       |

| INTP2     |              |                                                                                                                         | P23       |

| INTP3     |              |                                                                                                                         | P24       |

| INTP4     |              |                                                                                                                         | P25       |

| INTP5     |              |                                                                                                                         | P26       |

| INTP6     |              |                                                                                                                         | P27/TI    |

| NMI       | Input        | Edge-detected nonmaskable interrupt request input.                                                                      | P20       |

|           |              | The rising or falling edge can be selected for the valid edge by setting the mode register.                             |           |

| TI        | Input        | External count clock input pin to timer 1 (TM1).                                                                        | P27/INTP6 |

| RxD       | Input        | Serial data input pin to asynchronous serial interface (UART).                                                          | P31       |

| TxD       | Output       | Serial data output pin from asynchronous serial interface (UART).                                                       | P30       |

| SI        | Input        | Serial data input pin to clocked serial interface in 3-wire mode.                                                       | P33/SB1   |

| SO        | Output       | Serial data output pin from clocked serial interface in 3-wire mode.                                                    | P32/SB0   |

| SB0       | Input/Output | Serial data input/output pins to/from clocked serial interface in SBI mode.                                             | P32/SO    |

| SB1       |              |                                                                                                                         | P33/SI    |

| SCK       | Input/Output | Serial clock input/output pin to/from clocked serial interface.                                                         | P34       |

| AD0-AD7   | Input/Output | Multiplexed address/data bus used when external memory is added.                                                        | P40-P47   |

| A8-A15    | Output       | Address bus used when external memory is added.                                                                         | P50-P57   |

| RD        | Output       | Strobe signal output for external memory read operation.                                                                | P90       |

| WR        |              | Strobe signal output for external memory write operation.                                                               | P91       |

| TAS       | Output       | Control signal output pins to access turbo access manager (µPD71P301). Note                                             | P92       |

| TMD       |              |                                                                                                                         | P93       |

| TO00      | Output       | Pulse output from real-time pulse unit.                                                                                 | P80       |

| TO01      |              |                                                                                                                         | P81       |

| TO02      |              |                                                                                                                         | P82       |

| TO03      |              |                                                                                                                         | P83       |

| TO10      |              |                                                                                                                         | P84       |

| TO11      |              |                                                                                                                         | P85       |

| ASTB      | Output       | Timing signal output pin to externally latch low-order address information output from                                  | _         |

|           |              | AD0-AD7 for external memory access.                                                                                     |           |

| WDTO      | Output       | Signal output which indicates that watchdog timer generated non-maskable interrupt.                                     | _         |

| ĒA        | Input        | For $\mu$ PD78P322, normally connect the $\overline{EA}$ pin to $V_{DD}$ . When the $\overline{EA}$ pin is connected to | _         |

|           |              | Vss, the $\mu$ PD78P322 enters the ROMless mode and external memory is accessed.                                        |           |

|           |              | The EA pin level cannot be changed during operation.                                                                    |           |

**Note** Turbo access manager ( $\mu$ PD71P301) is available for maintenance purposes only.

\*

# (2) Non-Port Pins (2/2)

| Pin Name         | Input/Output                                                                            | Function                                                                                | Alternate |

|------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------|

|                  |                                                                                         |                                                                                         | Function  |

| AN0-AN7          | Input                                                                                   | Analog input to A/D converter.                                                          |           |

| AVREF            | Input                                                                                   | A/D converter reference voltage input.                                                  | _         |

| AV <sub>DD</sub> | _                                                                                       | A/D converter analog power supply.                                                      | _         |

| AVss             | Vss — A/D converter GND.                                                                |                                                                                         | _         |

| RESET            | Input                                                                                   | System reset input.                                                                     | _         |

| X1               | Input                                                                                   | Crystal resonator connection pin for system clock generation. To supply external clock, |           |

| X2               | X2 input to the X1 and input inverted signal to the X2 pin (X2 pin can be unconnected.) |                                                                                         |           |

| VDD              | V <sub>DD</sub> — Positive power supply pin.                                            |                                                                                         | _         |

| Vss              | _                                                                                       | GND pin.                                                                                | _         |

| NC               | _                                                                                       | No internal connection. Connect to Vss (can leave open).                                | _         |

# 1.2 PROM Programming Mode (RESET = H, AVDD = L)

| Pin Name         | Input/Output | Function                                                 |  |

|------------------|--------------|----------------------------------------------------------|--|

| AV <sub>DD</sub> | Input        | PROM programming mode setting.                           |  |

| RESET            |              |                                                          |  |

| A0-A14           | Input        | Address bus.                                             |  |

| D0-D7            | Input/Output | Data bus.                                                |  |

| CE               | Input        | PROM enable to PROM.                                     |  |

| OE               | Input        | Read strobe to PROM.                                     |  |

| V <sub>PP</sub>  | _            | Write power supply.                                      |  |

| V <sub>DD</sub>  |              | Positive power supply.                                   |  |

| Vss              |              | GND.                                                     |  |

| NC               |              | No internal connection. Connect to Vss (can leave open). |  |

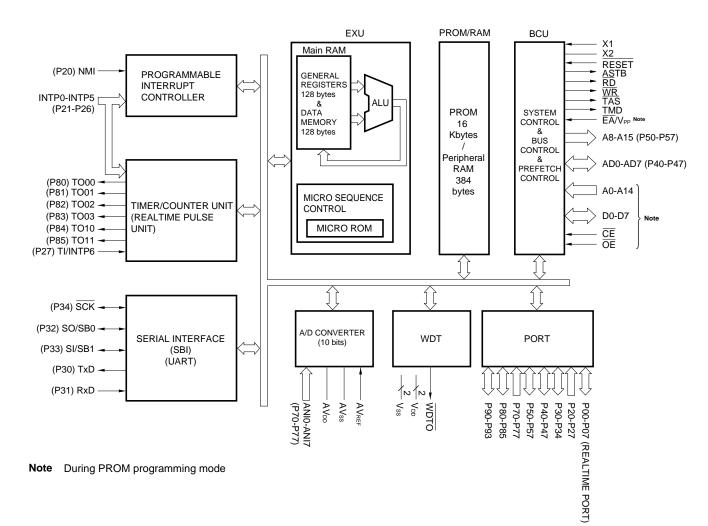

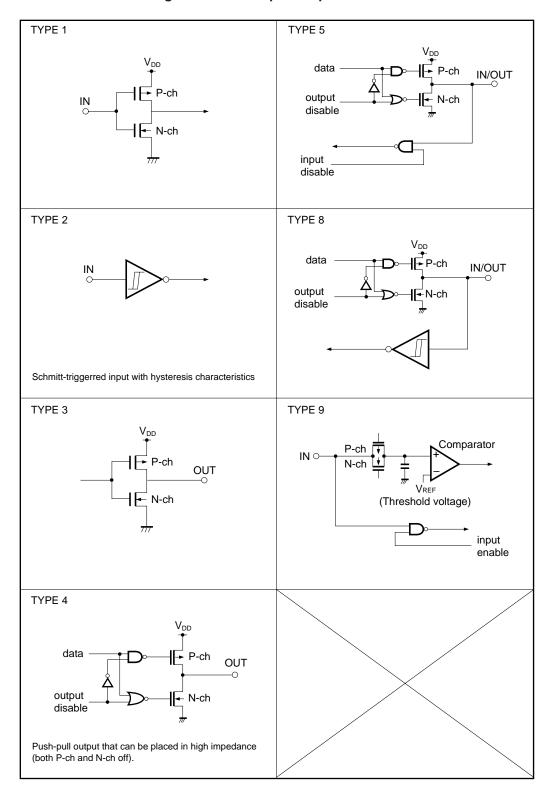

## 1.3 Pin Input/Output Circuits and Recommended Connection of Unused Pins

Table 1-1 and Figure 1-1 show the pin input/output circuit schematically.

Table 1-1. Pin Input/Output Circuits and Recommended Connection of Unused Pins

| Pin                 | Input/Output | Recommended connection of unused pins                                                    |

|---------------------|--------------|------------------------------------------------------------------------------------------|

|                     | circuit type |                                                                                          |

| P00/RTP0-P07/RTP7   | 5            | Input state: Independently connect to V <sub>DD</sub> or Vss via a resistor.             |

|                     |              | Output state: Leave Open.                                                                |

| P20/NMI             | 2            | Connect to Vss.                                                                          |

| P21/INTP0-P26/INTP5 |              |                                                                                          |

| P27/INTP6/TI        |              |                                                                                          |

| P30/TxD             | 5            | Input state: Independently connect to V <sub>DD</sub> or V <sub>SS</sub> via a resistor. |

| P31/RxD             |              | Output state: Leave Open.                                                                |

| P32/SO/SB0          | 8            |                                                                                          |

| P33/SI/SB1          |              |                                                                                          |

| P34/SCK             |              |                                                                                          |

| P40/AD0-P47/AD7     | 5            |                                                                                          |

| P50/A8-P57/A15      |              |                                                                                          |

| P70/AN0-P77/AN7     | 9            | Connect to Vss.                                                                          |

| P80/T000-P83/T003   | 5            | Input state: Independently connect to VDD or Vss via a resistor.                         |

| P84/TO10, P85/TO11  |              | Output state: Leave Open.                                                                |

| P90/RD              | 5            |                                                                                          |

| P91/WR              |              |                                                                                          |

| P92/TAS             |              |                                                                                          |

| P93/TMD             |              |                                                                                          |

| WDTO                | 3            | Leave Open.                                                                              |

| ASTB                | 4            |                                                                                          |

| EA                  | 1            | _                                                                                        |

| RESET               | 2            | _                                                                                        |

| AVDD                |              | Connect to V <sub>DD</sub> .                                                             |

| AVREF               | _            | Connect to Vss.                                                                          |

| AVss                |              |                                                                                          |

| Vpp                 | _            | Connect to VDD.                                                                          |

| NC                  |              | Connect to Vss (can leave open).                                                         |

Figure 1-1. Pin Input/Output Circuits

#### 2. DIFFERENCES BETWEEN $\mu$ PD78P322 and $\mu$ PD78322

The  $\mu$ PD78P322 is a version provided by replacing the  $\mu$ PD78322's on-chip mask ROM with one-time PROM or EPROM. Thus, the  $\mu$ PD78P322 and  $\mu$ PD78322 are the same in function except for the ROM specifications such as write or verify. Table 2-1 lists the differences between these two products.

This Data Sheet describes the PROM specification function. Refer to the  $\mu$ PD78322 documents for details of other functions.

Table 2-1. Differences between  $\mu$ PD78P322 and  $\mu$ PD78322

| Item Part Number          | μ <b>PD78P322</b>                                                                        |                                           | μPD78322             |  |

|---------------------------|------------------------------------------------------------------------------------------|-------------------------------------------|----------------------|--|

| Internal program memory   | One-time PROM EPROM                                                                      |                                           | Mask ROM             |  |

| (electrical program)      | (programmable only once)                                                                 | (programmable only once) (reprogrammable) |                      |  |

| PROM programming pin      | Contained                                                                                |                                           | Not contained        |  |

| Package                   | 68-pin plastic QFJ     68-pin ceramic WQFN                                               |                                           | 68-pin plastic QFJ   |  |

|                           | 74-pin plastic QFP                                                                       | • 74-pin ceramic WQFN                     | • 74-pin plastic QFP |  |

|                           | 80-pin plastic QFP     80-pin ceramic WQFN                                               |                                           | 80-pin plastic QFP   |  |

| Electrical specifications | Current dissipations are different.                                                      |                                           |                      |  |

| Others                    | Noise immunity and noise radiation differ because circuit complexity and mask layout are |                                           |                      |  |

|                           | different.                                                                               |                                           |                      |  |

\* Caution The noise immunity and noise radiation differ between the PROM and mask ROM versions. To replace the PROM version with the mask ROM version when shifting from experimental production to mass production, evaluate your system by using the CS version (not ES version) of the mask ROM version.

#### 3. PROM PROGRAMMING

The PROM incorporated in the  $\mu$ PD78P322 is a 16,384 × 8-bit electrically writable PROM. For programming, set the PROM programming mode by using the  $\overline{\text{RESET}}$  and AV<sub>DD</sub> pins.

The programming characteristics are compatible with the  $\mu$ PD27C256A programming characteristics.

Table 3-1. Pin Function in Programming Mode

| Function                  | Normal Operating Mode      | Programming Mode |  |

|---------------------------|----------------------------|------------------|--|

| Address input             | P00-P07, P80, P20, P81-P85 | A0-A14           |  |

| Data input                | P40-P47                    | D0-D7            |  |

| Chip enable/program pulse | P31                        | CE               |  |

| Output enable             | P30                        | ŌĒ               |  |

| Program voltage           | VPP                        |                  |  |

| Mode control              | RESET, AVDD                |                  |  |

#### 3.1 Operation Mode

To set the program write/verify mode, set  $\overline{RESET} = H$  and AVDD = L. For the mode, the operation mode can be selected by setting the  $\overline{CE}$  and  $\overline{OE}$  pins, as listed in Table 3-2.

To read the PROM contents, set the read mode.

Connect the unused pins exactly as indicated in Pin Configuration.

Table 3-2. PROM Programming Operation Mode

| Mode            | RESET | AVDD | CE | ŌE  | V <sub>PP</sub> | V <sub>DD</sub> | D0-D7          |

|-----------------|-------|------|----|-----|-----------------|-----------------|----------------|

| Program write   | Н     | L    | L  | Н   | +12.5 V         | +6 V            | Data input     |

| Program verify  |       |      | Н  | L   |                 |                 | Data output    |

| Program inhibit |       |      | Н  | Н   |                 |                 | High impedance |

| Read            |       |      | L  | L   | +5 V            | +5 V            | Data output    |

| Output disable  |       |      | L  | Н   |                 |                 | High impedance |

| Standby         |       |      | Н  | L/H |                 |                 | High impedance |

Caution When V<sub>PP</sub> is set to +12.5 V and V<sub>DD</sub> is set to +6V, setting both  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  to L is prohibited.

#### 3.2 PROM Write Procedure

The write procedure into PROM is as follows:

- (1) Fix RESET = H and AVDD = L. Connect other unused pins exactly as indicated in section "Pin Configuration."

- (2) Supply +6 V to the VDD and +12.5 V to the VPP pin.

- (3) Supply an initial address.

- (4) Supply write data.

- (5) Supply 1 ms program pulse (active low) to the  $\overline{CE}$  pin.

- (6) Execute the verify mode. Check whether or not the write data is written normally.

- When it is written normally: Proceed to step (8).

- When it is not written normally: Repeat steps (4) to (6).

If the data is not written normally after 25 repetitions of the steps, proceed to step (7).

- (7) Assume the device to be defective. Stop write operation.

- (8) Supply write data and X (number of steps (4) to (6) repetitions) x 3 ms program pulses (additional write).

- (9) Increment the address.

- (10) Repeat steps (4) to (9) to the last address.

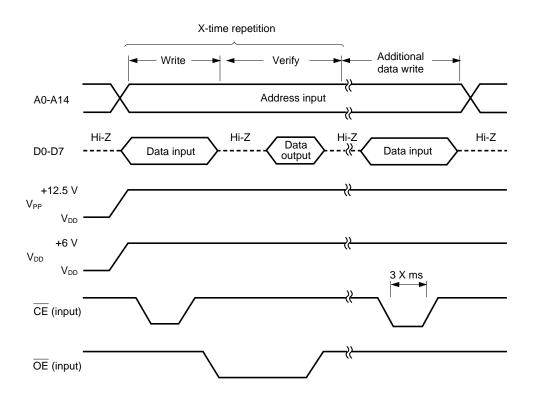

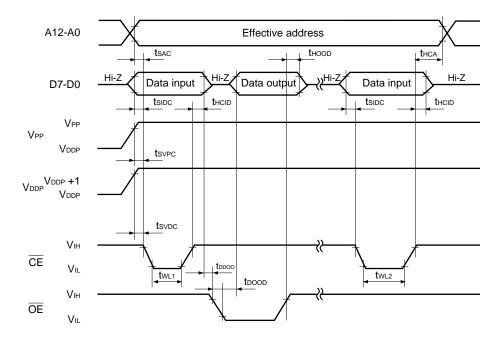

Figure 3-1 shows the PROM Write/Verify Timing Steps (2) to (8) above.

Figure 3-1. PROM Write/Verify Timing

Figure 3-2. Write Procedure Flowchart

#### 3.3 PROM Read Procedure

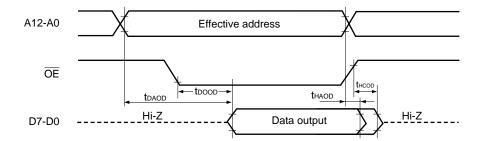

The read procedure of the PROM contents into the external data bus (D0-D7) is as follows.

- (1) Fix RESET = H and AVDD = L. Connect other unused pins exactly as indicated in Pin Configuration.

- (2) Supply +5 V to the VDD and VPP pins.

- (3) Input the address of the data to be read to the A0-A14 pins.

- (4) Execute the read mode.

- (5) The data is output to the D0-D7 pins.

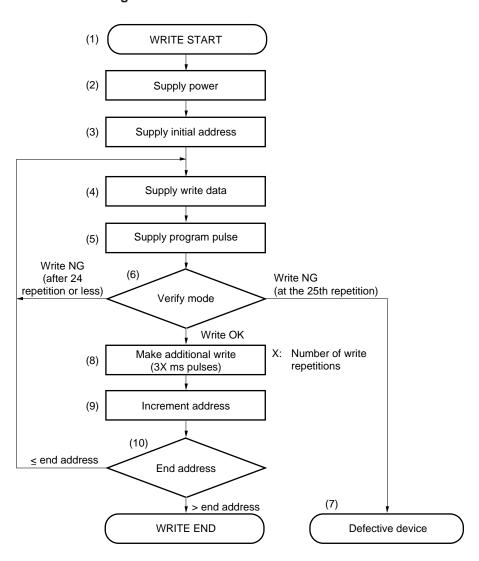

Figure 3-3 shows the PROM read timing steps (2) to (5) above.

Figure 3-3. PROM Read Timing

#### 4. ERASURE CHARACTERISTICS (FOR $\mu$ PD78P322K/KC/KD ONLY)

The data written into the  $\mu$ PD78P322K/KC/KD program memory can be erased (FFH) and new data can be rewritten into the memory.

To erase data, apply light with a wavelength shorter than 400 nm to the window. Normally, apply ultraviolet rays having the 254-nm wavelength. The radiation amount required to completely erase data is as follows:

- Ultraviolet strength x erasure time: 15 W•s/cm² or more

- Erasure time: 15 to 20 minutes when a 12,000  $\mu$ W/cm<sup>2</sup> ultraviolet lamp is used. However, the time may be prolonged due to ultraviolet lamp performance deterioration, dirty window, etc.

For erasure, place an ultraviolet lamp at a position within 2.5 cm from the window. If a filter is attached to the ultraviolet lamp, remove the filter before applying ultraviolet rays.

#### 5. OPAQUE FILM ON ERASURE WINDOW (FOR $\mu$ PD78P322K/KC/KD ONLY)

If the  $\mu$ PD78P322K/KC/KD window is exposed to sunlight or fluorescent lamp light for hours, EPROM data may be erased and the internal circuit may operate erroneously. To prevent such accidents from occurring, put a protective seal on the window.

A protective seal whose quality is guaranteed by NEC is attached to every EPROM version with window at shipment.

#### 6. ONE-TIME PROM VERSION SCREENING

The one-time PROM versions ( $\mu$ PD78P322GF-3B9, 78P322GJ-5BJ, 78P322L) cannot be completely tested by NEC for shipment because of their structure. For screening, it is recommended to verify PROM after storing the necessary data under the following conditions:

| Storage temperature | Storage time |  |

|---------------------|--------------|--|

| 125°C               | 24 hours     |  |

NEC provides chargeable services ranging from one-time PROM writing to marking, screening and verification for QTOP microcontroller products. For details, contact an NEC sales representative.

#### 7. ELECTRICAL SPECIFICATIONS

### **Absolute Maximum Ratings** (TA = 25 °C)

| Parameter                     | Symbol          | Test Condit                        | tions                              | Ratings                       | Unit |

|-------------------------------|-----------------|------------------------------------|------------------------------------|-------------------------------|------|

| Power supply voltage          | V <sub>DD</sub> |                                    |                                    | -0.5 to +7.0                  | V    |

|                               | AVDD            |                                    |                                    | -0.5 to V <sub>DD</sub> +0.5  | V    |

|                               | V <sub>PP</sub> |                                    |                                    | -0.5 to +13.5                 | V    |

|                               | AVss            |                                    |                                    | -0.5 to +0.5                  | V    |

| Input voltage                 | VII             | Note 1                             | Note 1 -                           |                               | V    |

|                               | V <sub>I2</sub> | P20/NIM (A                         | (9) PIN                            | -0.5 to +13.5                 | V    |

| Output voltage                | Vo              |                                    |                                    | -0.5 to V <sub>DD</sub> +0.5  | V    |

| Output current, low           | Іоь             | All output pins                    |                                    | 4.0                           | mA   |

|                               |                 | Total for all                      | pins                               | 90                            | mA   |

| Output current, high          | Іон             | All output pins Total for all pins |                                    | -1.0                          | mA   |

|                               |                 |                                    |                                    | -20                           | mA   |

| Analog input voltage          | VIAN            | Note 2                             | AVDD > VDD                         | -0.5 to V <sub>DD</sub> +0.5  | V    |

|                               |                 |                                    | $V_{DD} \ge AV_{DD}$               | -0.5 to AV <sub>DD</sub> +0.5 |      |

| A/D converter reference       | AVREF           |                                    | AVDD > VDD                         | -0.5 to V <sub>DD</sub> +0.3  | V    |

| input voltage                 |                 |                                    | V <sub>DD</sub> ≥ AV <sub>DD</sub> | -0.5 to AV <sub>DD</sub> +0.3 |      |

| Operating ambient temperature | TA              |                                    |                                    | -10 to +70                    | °C   |

| Storage temperature           | Tstg            |                                    |                                    | -65 to +150                   | °C   |

Notes 1. Pins except for P20/NMI (A9), P70/AN0-P77/AN7

- **2.** P70/AN0-P77/AN7

- \* Caution Product quality may suffer if the absolute maximum rating is exceeded for even a single parameter, even momentarily. In other words, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions which ensure that the absolute maximum ratings are not exceeded.

## **Recommended Operating Conditions**

| Oscillation frequency | TA            | V <sub>DD</sub> |

|-----------------------|---------------|-----------------|

| 8 MHz ≤ fxx ≤ 16 MHz  | –10 to +70 °C | +5.0 V ±5%      |

Capacitance (TA = 25 °C, Vss = VDD = 0 V)

| Parameter          | Symbol | Test Conditions                 | MIN. | TYP. | MAX. | Unit |

|--------------------|--------|---------------------------------|------|------|------|------|

| Input capacitance  | Сі     | f = 1 MHz                       |      |      | 10   | pF   |

| Output capacitance | Со     | Unmeasured pins returned to 0 V |      |      | 20   | pF   |

| I/O capacitance    | Сю     |                                 |      |      | 20   | pF   |

## Oscillator Characteristics (TA = -10 to +70 °C, VDD = +5 V $\pm 5$ %, Vss = 0 V)

| Resonator                    | Recommended Circuit                                       | Parameter                                                    | MIN. | MAX. | Unit |

|------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|------|------|------|

| Ceramic or crystal resonator | X2 X1 V <sub>SS</sub> ——————————————————————————————————— | Oscillation frequency (fxx)                                  | 8    | 16   | MHz  |

| External clock               | X1 X2  HCMOS Inverter  or  X1 X2                          | X1 input frequency (fx)  X1 input rise, fall time (fxR, txF) | 8    | 16   | MHz  |

|                              | Open HCMOS                                                | X1 input high, low level width                               | 25   | 80   | ns   |

|                              | Inverter                                                  | (twxh, twxL)                                                 |      |      |      |

Caution When using the system clock oscillator, wire the portion enclosed in broken lines in the figure as follows to avoid adverse influences on the wiring capacitance:

- · Keep the wiring length as short as possible.

- Do not cross the wiring over the other signal lines. Do not route the wiring in the vicinity of lines through which a high fluctuating current flows.

- Always keep the ground point of the capacitor of the oscillator circuit at the same potential as

Vss. Do not connect the power source pattern through which a high current flows.

- Do not extract signals from the oscillator.

## **Recommended Oscillator Constants**

## Ceramic resonator

| Manufacturer Name | Part Number    | Frequency | Recommended |          |

|-------------------|----------------|-----------|-------------|----------|

|                   |                | [MHz]     | Constants   |          |

|                   |                |           | C1 [pF]     | C2 [pF]  |

| MURATA            | CSA8.00MT      | 8.0       | 30          | 30       |

|                   | CSA12.0MT      | 12.0      |             |          |

|                   | CSA14.74MXZ040 | 14.74     | 15          | 15       |

|                   | CSA16.00MX040  | 16.0      |             |          |

|                   | CST8.00MTW     | 8.0       | Internal    | Internal |

|                   | CST12.0MTW     | 12.0      |             |          |

|                   | CST14.74MXW0C3 | 14.74     |             |          |

|                   | CST16.00MXW0C3 | 16.0      |             |          |

# Crystal resonator

| Manufacturer Name | Part Number | Frequency | Recommended |         |

|-------------------|-------------|-----------|-------------|---------|

|                   |             | [MHz]     | Constants   |         |

|                   |             |           | C1 [pF]     | C2 [pF] |

| KINSEKI           | HC49/U-S    | 8 to 16   | 10          | 10      |

|                   | HC49/U      |           |             |         |

# **DC Characteristics** (TA = -10 to +70 °C, VDD = +5 V $\pm 5\%$ , Vss = 0 V)

| Parameter                            | Symbol           | Test Condition                     | s                 | MIN.                 | TYP. | MAX. | Unit |

|--------------------------------------|------------------|------------------------------------|-------------------|----------------------|------|------|------|

| Input voltage, low                   | VIL              |                                    |                   | 0                    |      | 0.8  | V    |

| Input voltage, high                  | V <sub>IH1</sub> | Note 1                             |                   | 2.2                  |      |      | V    |

|                                      | V <sub>IH2</sub> | Note 2                             |                   | 0.8V <sub>DD</sub>   |      |      |      |

| Output voltage, low                  | Vol              | IoL = 2.0 mA                       |                   |                      |      | 0.45 | V    |

| Output voltage, high                 | Vон              | Іон = -400 μΑ                      |                   | V <sub>DD</sub> -1.0 |      |      | V    |

| Input leakage current                | lu               | $0 \text{ V} \leq V_I \leq V_{DD}$ |                   |                      |      | ±10  | μΑ   |

| Output leakage current               | Іьо              | 0 V ≤ Vo ≤ VDD                     | )                 |                      |      | ±10  | μΑ   |

| V <sub>DD</sub> power supply current | I <sub>DD1</sub> | Operation mod                      | le                |                      | 40   | 65   | mA   |

|                                      | I <sub>DD2</sub> | HALT mode                          |                   |                      | 20   | 35   | mA   |

| Data retention voltage               | VDDDR            | STOP mode                          |                   | 2.5                  |      |      | V    |

| Data retention current               | Idddr            | STOP mode                          | VDDDR = 2.5 V     |                      | 2    | 10   | μΑ   |

|                                      |                  |                                    | VDDDR = 5.0 V ±5% |                      | 10   | 50   | μΑ   |

#### Notes 1. Pins other than mentioned in Note 2.

**2.** RESET, X1, X2, P20/NMI, P21/INTP0, P22/INTP1, P23/INTP2, P24/INTP3, P25/INTP4, P26/INTP5, P27/INTP6/TI, P32/SO/SB0, P33/SI/SB1, or P34/SCK pins.

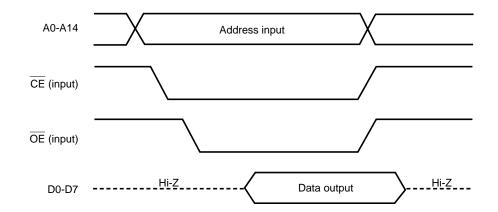

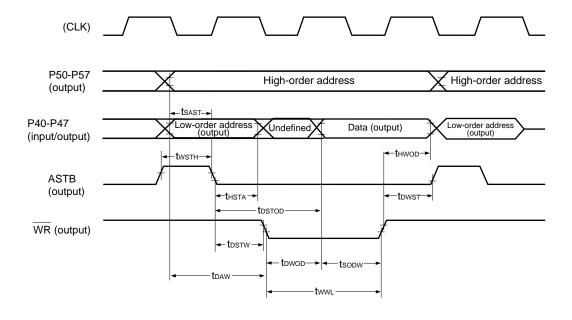

**\*** AC Characteristics (TA = -10 to +70 °C, VDD = +5 V  $\pm 5\%$ , Vss = 0 V)

Discontinuous read/write operation (when general-purpose memory is connected)

| Parameter                                                             | Symbol | Test Conditions | MIN. | MAX. | Unit |

|-----------------------------------------------------------------------|--------|-----------------|------|------|------|

| System clock cycle time                                               | tсүк   |                 | 125  | 250  | ns   |

| Address setup time (to ASTB $\downarrow$ )                            | tsast  |                 | 32   |      | ns   |

| Address hold time (from ASTB $\downarrow$ )                           | thsta  |                 | 32   |      | ns   |

| $Address \to \overline{RD} \downarrow delay \ time$                   | tdar   |                 | 85   |      | ns   |

| $\overline{RD} \downarrow 	o$ address float time                      | tfra   |                 |      | 0    | ns   |

| Address → data input time                                             | tdaid  |                 |      | 222  | ns   |

| $\overline{ m RD} \downarrow  ightarrow$ data input time              | torio  |                 |      | 112  | ns   |

| $ASTB \downarrow \to \overline{RD} \downarrow delay time$             | tostr  |                 | 42   |      | ns   |

| Data hold time (from RD ↑)                                            | thrid  |                 | 0    |      | ns   |

| $\overline{RD} \uparrow \to address$ active time                      | tdra   |                 | 50   |      | ns   |

| RD low level width                                                    | twrL   |                 | 157  |      | ns   |

| ASTB high level width                                                 | twsтн  |                 | 37   |      | ns   |

| Address $ ightarrow \overline{WR} \downarrow delay time$              | tdaw   |                 | 85   |      | ns   |

| ASTB $\downarrow$ $\rightarrow$ data output time                      | tostod |                 |      | 102  | ns   |

| $\overline{ m WR} \downarrow  ightarrow$ data output time             | towod  |                 |      | 40   | ns   |

| $ASTB \downarrow 	o \overline{WR} \downarrow delay \; time$           | tostw  |                 | 42   |      | ns   |

| Data setup time (to WR ↑)                                             | tsodw  |                 | 147  |      | ns   |

| Data hold time (from WR ↑)                                            | thwod  |                 | 32   |      | ns   |

| $\overline{ m WR} \uparrow  ightarrow  m ASTB \uparrow  m delay time$ | towst  |                 | 42   |      | ns   |

| WR low level width                                                    | twwL   |                 | 157  |      | ns   |

## tcүк-Dependent Bus Timing Definition

| Parameter | Calculation expression | MIN./MAX. | Unit |

|-----------|------------------------|-----------|------|

| tsast     | 0.5T – 30              | MIN.      | ns   |

| thsta     | 0.5T - 30              | MIN.      | ns   |

| tdar      | T – 40                 | MIN.      | ns   |

| tdaid     | (2.5 + n) T – 90       | MAX.      | ns   |

| torid     | (1.5 + n) T – 75       | MAX.      | ns   |

| tostr     | 0.5T - 20              | MIN.      | ns   |

| tdra      | 0.5T – 12              | MIN.      | ns   |

| twrl      | (1.5 + n) T – 30       | MIN.      | ns   |

| twsтн     | 0.5T – 25              | MIN.      | ns   |

| tdaw      | T – 40                 | MIN.      | ns   |

| tostod    | 0.5T + 40              | MAX.      | ns   |

| tostw     | 0.5T – 20              | MIN.      | ns   |

| tsodw     | 1.5T – 40              | MIN.      | ns   |

| thwod     | 0.5T - 30              | MIN.      | ns   |

| towst     | 0.5T – 20              | MIN.      | ns   |

| twwL      | (1.5 + n) T – 30       | MIN.      | ns   |

**Remarks 1.** T = tcyk = 1/fclk (fclk is the internal system clock frequency).

- 2. n is the number of wait cycles defined by user software.

- 3. Only parameters listed in the table are dependent on  $tcy\kappa$ .

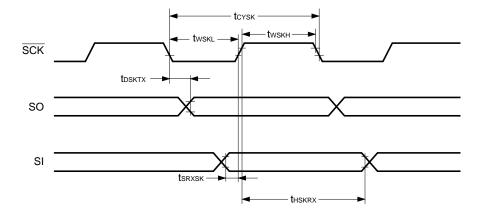

# **Serial Operation** (TA = -10 to +70 °C, VDD = +5 V $\pm 5\%$ , Vss = 0 V)

| Parameter                                     | Symbol | Test Condition | ns                   | MIN. | MAX. | Unit |

|-----------------------------------------------|--------|----------------|----------------------|------|------|------|

| Serial clock cycle time                       | tcysk  | SCK Output     | Internal divide by 8 | 1    |      | μs   |

|                                               |        | SCK Input      | External clock       | 1    |      | μs   |

| Serial clock high-level width                 | twskL  | SCK Output     | Internal divide by 8 | 420  |      | ns   |

|                                               |        | SCK Input      | External clock       | 420  |      | ns   |

| Serial clock high-level width                 | twskH  | SCK Output     | Internal divide by 8 | 420  |      | ns   |

|                                               |        | SCK Input      | External clock       | 420  |      | ns   |

| SI setup time (to SCK ↑)                      | tsrxsk |                |                      | 80   |      | ns   |

| SI hold time (from SCK ↑)                     | thskrx |                |                      | 80   |      | ns   |

| $\overline{SCK} \downarrow \to SO$ delay time | tosktx | R = 1 kΩ, C =  | = 100 pF             |      | 210  | ns   |

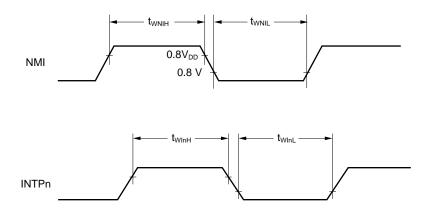

# Other operations (TA = -10 to $+70^{\circ}$ C, VDD = +5 V $\pm 5\%$ , Vss = 0 V)

| Parameter                   | Symbol | Test Conditions           | MIN. | MAX. | Unit |

|-----------------------------|--------|---------------------------|------|------|------|

| NMI high, low-level width   | twnih, |                           | 5    |      | μs   |

|                             | twnil  |                           |      |      |      |

| INTP0 high, low-level width | twioн, |                           | 8T   |      | tcyk |

|                             | twioL  |                           |      |      |      |

| INTP1 high, low-level width | twi1н, |                           | 8T   |      | tcyk |

|                             | twi1L  |                           |      |      |      |

| INTP2 high, low-level width | twizh, |                           | 8T   |      | tcyk |

|                             | twi2L  |                           |      |      |      |

| INTP3 high, low-level width | twiзн, |                           | 8T   |      | tcyk |

|                             | twisL  |                           |      |      |      |

| INTP4 high, low-level width | twi4н, |                           | 8T   |      | tcyk |

|                             | tw14L  |                           |      |      |      |

| INTP5 high, low-level width | twisн, |                           | 8T   |      | tcyk |

|                             | twisL  |                           |      |      |      |

| INTP6 high, low-level width | twi6н, |                           | 8T   |      | tcyk |

|                             | twicL  |                           |      |      |      |

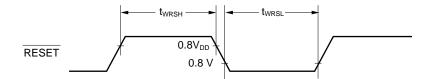

| RESET high, low-level width | twrsh, |                           | 5    |      | μs   |

|                             | twrsL  |                           |      |      |      |

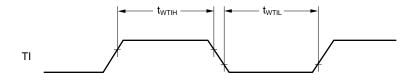

| TI high, low-level width    | twтıн, | TM1                       | 8T   |      | tcyk |

|                             | twTIL  | In the event counter mode |      |      |      |

## A/D Converter (TA = -10 to +70°C, VDD = +5 V $\pm 5$ %, Vss = AVss = 0 V, VDD -0.5 V $\leq$ AVDD $\leq$ VDD)

| Parameter                       | Symbol | Test Conditions             |                  | MIN. | TYP. | MAX. | Unit |

|---------------------------------|--------|-----------------------------|------------------|------|------|------|------|

| Resolution                      |        |                             |                  | 10   |      |      | bit  |

| Total error Note1               |        | 4.5 V ≤ AVREF ≤             | AV <sub>DD</sub> |      |      | ±0.4 | %FSR |

|                                 |        | 3.4 V ≤ AVREF ≤             | AVDD             |      |      | ±0.7 | %FSR |

| Quantization error              |        |                             |                  |      |      | ±1/2 | LSB  |

| Conversion time                 | tconv  |                             |                  | 144  |      |      | tcyk |

| Sampling time                   | tsamp  |                             |                  | 24   |      |      | tcyk |

| Zero scale error Note1          |        | 4.5 V ≤ AVREF ≤             | AV <sub>DD</sub> |      | +1.5 | ±2.5 | LSB  |

|                                 |        | 3.4 V ≤ AV <sub>REF</sub> ≤ | AV <sub>DD</sub> |      | +1.5 | ±4.5 | LSB  |

| Fullscale error Note1           |        | 4.5 V ≤ AVREF ≤             | AVDD             |      | +1.5 | ±2.5 | LSB  |

|                                 |        | 3.4 V ≤ AVREF ≤             | AV <sub>DD</sub> |      | +1.5 | ±4.5 | LSB  |

| Nonlinear error Note1           |        | 4.5 V ≤ AVREF ≤             | AV <sub>DD</sub> |      | +1.5 | ±2.5 | LSB  |

|                                 |        | 3.4 V ≤ AVREF ≤             | AV <sub>DD</sub> |      | +1.5 | ±4.5 | LSB  |

| Analog input voltage Note2      | VIAN   |                             |                  | -0.3 |      | AVDD | V    |

| Basic voltage                   | AVREF  |                             |                  | 3.4  |      | AVDD | V    |

| AVREF current                   | AIREF  |                             |                  |      | 1.0  | 3.0  | mA   |

| AV <sub>DD</sub> supply current | Aldd   |                             |                  |      | 2.0  | 6.0  | mA   |

| A/D converter data              | Aldddr | STOP mode                   | AVDDDR = 2.5 V   |      | 2.0  | 10   | μΑ   |

| retention current               |        |                             | AVDDDR = 5 V±5%  |      | 10   | 50   | μΑ   |

### Notes 1. Quantization error is excluded.

2. When  $-0.3~V \le V_{IAN} \le 0~V$ , conversion result is 000H. When 0 V < V\_{IAN} < AV\_{REF}, conversion is executed with 10-bit resolution. When  $AV_{REF} \le V_{IAN} \le AV_{DD}$ , conversion result is 3FFH.

\*

## **Discontinuous Read Operation**

## **Discontinuous Write Operation**

# **Serial Operation**

# **Interrupt Input Timing**

**Remark** n = 0-6

# **Reset Input Timing**

# TI Pin Input Timing

# DC Programming Characteristics (TA = 25 $\pm$ 5 $^{\circ}$ C, Vss = 0 V)

| Parameter                             | Symbol          | Symbol<br>Note1 | Test conditions                                                            | MIN.       | TYP. | MAX.                  | Unit |

|---------------------------------------|-----------------|-----------------|----------------------------------------------------------------------------|------------|------|-----------------------|------|

| Input voltage, high                   | Vін             | ViH             |                                                                            | 2.2        |      | V <sub>DDP</sub> +0.3 | V    |

| Input voltage, low                    | VIL             | VIL             |                                                                            | -0.3       |      | 0.8                   | V    |

| Input leakage current                 | ILIP            | Li              | $0 \le V_{I} \le V_{DDP}$ Note 2                                           |            |      | ±10                   | μΑ   |

| Output voltage, high                  | Vон             | Vон             | $I_{OH} = -400 \ \mu A$                                                    | 2.4        |      |                       | V    |

| Output voltage, low                   | Vol             | Vol             | IoL = 2.0 mA                                                               |            |      | 0.45                  | V    |

| Input current                         | I <sub>A9</sub> | _               | A9 (P20/NMI) pin                                                           |            |      | ±10                   | μΑ   |

| Output leakage current                | ILO             | _               | $0 \le V_0 \le V_{DDP}, \overline{OE} = V_{IN}$                            |            |      | 10                    | μΑ   |

| PROG pin high voltage input current   | IIP             | _               |                                                                            |            |      | ±10                   | μΑ   |

| V <sub>DDP</sub> power supply voltage | VDDP            | V <sub>DD</sub> | Program memory write mode                                                  | 5.75       | 6.0  | 6.25                  | V    |

|                                       |                 |                 | Program memory read mode                                                   | 4.5        | 5.0  | 5.5                   | V    |

| VPP power supply voltage              | V <sub>PP</sub> | VPP             | Program memory write mode                                                  | 12.2       | 12.5 | 12.8                  | V    |

|                                       |                 |                 | Program memory read mode                                                   | VPP = VDDP |      | V                     |      |

| V <sub>DDP</sub> power supply current | IDD             | IDD             | Program memory write mode                                                  |            | 10   | 30                    | mA   |

|                                       |                 |                 | Program memory read mode $\overline{CE} = V_{IL}, V_{I} = V_{IH}$          |            | 10   | 30                    | mA   |

| VPP power supply current              | Ірр             | Ірр             | Program memory write mode $\overline{CE} = V_{IL}, \overline{OE} = V_{IH}$ |            | 10   | 30                    | mA   |

|                                       |                 |                 | Program memory read mode                                                   |            | 1    | 100                   | μΑ   |

**Notes 1.** Corresponding  $\mu$ PD27C256A symbols.

2. VDDP is VDD pin during the programming mode.

# AC Programming Characteristics (TA = 25 $\pm$ 5 °C, Vss = 0 V)

| Parameter                                                 | Symbol        | Symbol | Test conditions | MIN. | TYP. | MAX.  | Unit |

|-----------------------------------------------------------|---------------|--------|-----------------|------|------|-------|------|

|                                                           |               | Note   |                 |      |      |       |      |

| Address setup time (to $\overline{\sf CE}\ \downarrow$ )  | tsac          | tas    |                 | 2    |      |       | μs   |

| $Data 	o \overline{OE} \downarrow delay \; time$          | todoo         | toes   |                 | 2    |      |       | μs   |

| Input data setup time (to CE ↓)                           | tsidc         | tos    |                 | 2    |      |       | μs   |

| Address hold time (from CE ↑)                             | thca          | tан    |                 | 2    |      |       | μs   |

| Input data hold time (from CE ↑)                          | thcid         | tон    |                 | 2    |      |       | μs   |

| Output data hold time (from OE ↑)                         | thood         | tor    |                 | 0    |      | 130   | ns   |

| V <sub>PP</sub> setup time (to $\overline{\text{CE}}$ ↓)  | tsvpc         | tvps   |                 | 2    |      |       | μs   |

| V <sub>DDP</sub> setup time (to $\overline{\text{CE}}$ ↓) | tsvdc         | tvps   |                 | 2    |      |       | μs   |

| Initial program pulse width                               | twL1          | tpw    |                 | 0.95 | 1.0  | 1.05  | ms   |

| Additional program pulse width                            | twL2          | topw   |                 | 2.85 |      | 78.75 | ms   |

| Address → data output time                                | <b>t</b> DAOD | tacc   | OE = VIL        |      |      | 2     | μs   |

| $\overline{OE} \downarrow \to data$ output time           | tDOOD         | toe    |                 |      |      | 1     | μs   |

| Data hold time (from OE ↑)                                | tнсор         | tof    |                 | 0    |      | 130   | ns   |

| Data hold time (from address)                             | thaod         | tон    | OE = VIL        | 0    |      |       | ns   |

**Note** Corresponding  $\mu$ PD27C256A symbols.

## **PROM Write Mode Timing**

Cautions 1. Apply VDDP before VPP and remove it after VPP.

2. VPP must not exceed +13 V, including the overshoot.

## **PROM Read Mode Timing**

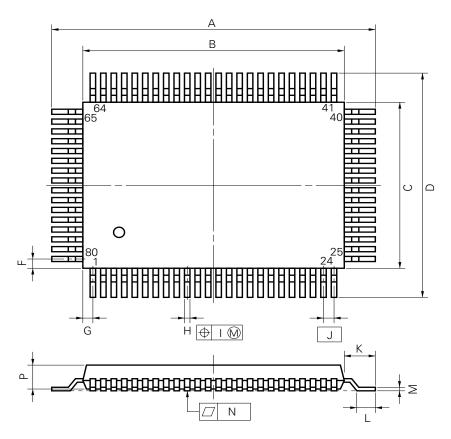

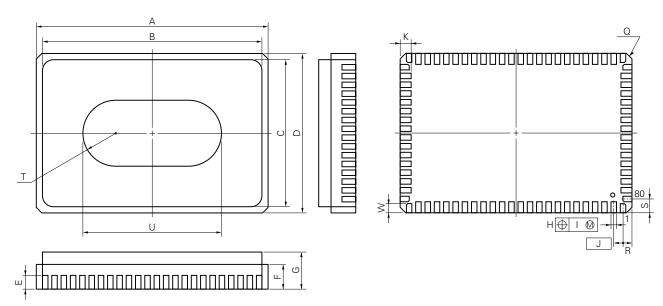

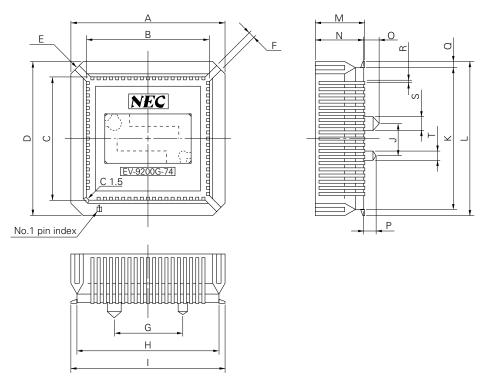

### 8. PACKAGE DRAWINGS

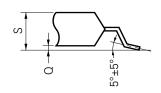

## 80 PIN PLASTIC QFP (14×20)

detail of lead end

NOTE

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

P80GF-80-3B9-2

| ITEM | MILLIMETERS                            | INCHES                    |  |  |  |  |

|------|----------------------------------------|---------------------------|--|--|--|--|

| А    | 23.6±0.4                               | 0.929±0.016               |  |  |  |  |

| В    | 20.0±0.2                               | $0.795^{+0.009}_{-0.008}$ |  |  |  |  |

| С    | 14.0±0.2                               | $0.551^{+0.009}_{-0.008}$ |  |  |  |  |

| D    | 17.6±0.4                               | 0.693±0.016               |  |  |  |  |

| F    | 1.0                                    | 0.039                     |  |  |  |  |

| G    | 0.8                                    | 0.031                     |  |  |  |  |

| Н    | 0.35±0.10                              | $0.014^{+0.004}_{-0.005}$ |  |  |  |  |

| I    | 0.15                                   | 0.006                     |  |  |  |  |

| J    | 0.8 (T.P.)                             | 0.031 (T.P.)              |  |  |  |  |

| K    | 1.8±0.2                                | 0.071+0.008               |  |  |  |  |

| L    | 0.8±0.2                                | 0.031+0.009               |  |  |  |  |

| М    | 0.15 <sup>+0.10</sup> <sub>-0.05</sub> | 0.006+0.004               |  |  |  |  |

| N    | 0.15                                   | 0.006                     |  |  |  |  |

| Р    | 2.7                                    | 0.106                     |  |  |  |  |

| Q    | 0.1±0.1                                | 0.004±0.004               |  |  |  |  |

| S    | 3.0 MAX.                               | 0.119 MAX.                |  |  |  |  |

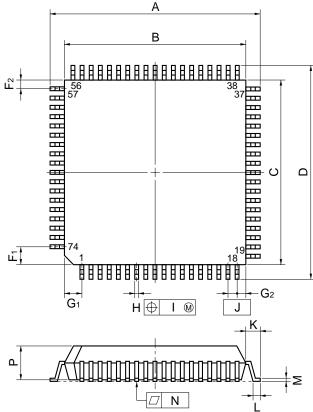

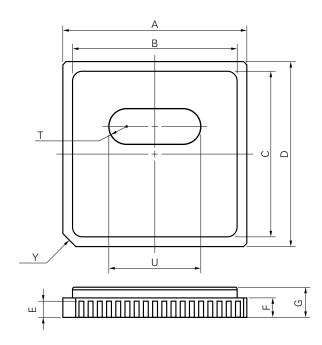

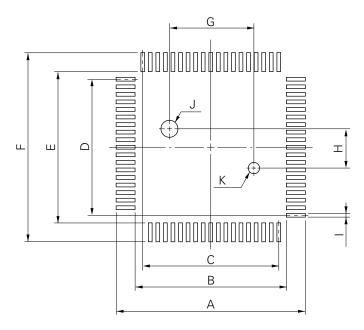

# 74 PIN PLASTIC QFP (□20)

## NOTE

Each lead centerline is located within 0.20 mm (0.008 inch) of its true position (T.P.) at maximum material condition.

detail of lead end

| MILLIMETERS                    | INCHES                                                                                                                                    |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 23.2±0.4                       | $0.913^{+0.017}_{-0.016}$                                                                                                                 |

| 20.0±0.2                       | $0.787^{+0.009}_{-0.008}$                                                                                                                 |

| 20.0±0.2                       | $0.787^{+0.009}_{-0.008}$                                                                                                                 |

| 23.2±0.4                       | 0.913+0.017                                                                                                                               |

| 2.0                            | 0.079                                                                                                                                     |

| 1.0                            | 0.039                                                                                                                                     |

| 2.0                            | 0.079                                                                                                                                     |

| 1.0                            | 0.039                                                                                                                                     |

| 0.40±0.10                      | $0.016^{+0.004}_{-0.005}$                                                                                                                 |

| 0.20                           | 0.008                                                                                                                                     |

| 1.0 (T.P.)                     | 0.039 (T.P.)                                                                                                                              |

| 1.6±0.2                        | 0.063±0.008                                                                                                                               |

| 0.8±0.2                        | $0.031^{+0.009}_{-0.008}$                                                                                                                 |

| 0.15 <sup>+0.10</sup><br>-0.05 | $0.006^{+0.004}_{-0.003}$                                                                                                                 |

| 0.10                           | 0.004                                                                                                                                     |

| 3.7                            | 0.146                                                                                                                                     |

| 0.1±0.1                        | 0.004±0.004                                                                                                                               |

| 5°±5°                          | 5°±5°                                                                                                                                     |

| 4.0 MAX.                       | 0.158 MAX.                                                                                                                                |

|                                | 23.2±0.4  20.0±0.2  20.0±0.2  23.2±0.4  2.0  1.0  2.0  1.0  0.40±0.10  0.20  1.0 (T.P.)  1.6±0.2  0.8±0.2  0.15+0.10  3.7  0.1±0.1  5°±5° |

S74GJ-100-5BJ-3

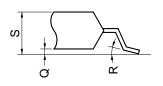

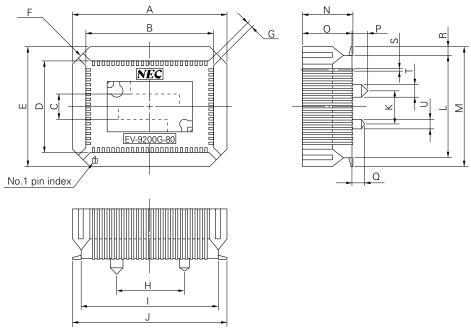

## 68 PIN PLASTIC QFJ (□950 mil)

NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

P68L-50A1-2 ITEM **MILLIMETERS INCHES** 25.2±0.2 0.992±0.008 В 24.20 0.953 С 24.20 0.953 D 25.2±0.2 0.992±0.008  $0.076^{+0.007}_{-0.006}$ Ε 1.94±0.15 F 0.024 0.6  $0.173^{+0.009}_{-0.008}$ G 4.4±0.2  $0.110^{+0.009}_{-0.008}$ Н 2.8±0.2 0.035 MIN. Τ 0.9 MIN. J 3.4 0.134 1.27 (T.P.) 0.050 (T.P.) Κ  $0.016\substack{+0.004 \\ -0.005}$ Μ  $0.40 \pm 1.0$ Ν 0.12 0.005 Ρ 23.12±0.20  $0.910^{+0.009}_{-0.008}$ Q 0.006 0.15 Т R 0.8 R 0.031  $0.20^{+0.10}_{-0.05}$  $0.008^{+0.004}_{-0.002}$ U

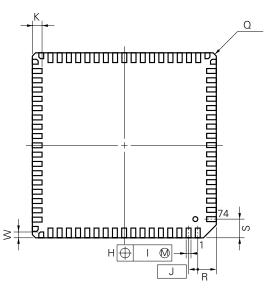

## **80 PIN CERAMIC WQFN**

## NOTE

Each lead centerline is located within 0.08 mm (0.003 inch) of its true position (T.P.) at maximum material condition.

## X80KW-80A-1

| ITEM | MILLIMETERS | INCHES       |

|------|-------------|--------------|

| А    | 20.0±0.4    | 0.787+0.017  |

| В    | 19.0        | 0.748        |

| С    | 13.2        | 0.520        |

| D    | 14.2±0.4    | 0.559±0.016  |

| Е    | 1.64        | 0.065        |

| F    | 2.14        | 0.084        |

| G    | 4.064 MAX.  | 0.160 MAX.   |

| Н    | 0.51±0.10   | 0.020±0.004  |

| I    | 0.08        | 0.003        |

| J    | 0.8 (T.P.)  | 0.031 (T.P.) |

| K    | 1.0±0.2     | 0.039+0.009  |

| Q    | C 0.5       | C 0.020      |

| R    | 0.8         | 0.031        |

| S    | 1.1         | 0.043        |

| Т    | R 3.0       | R 0.118      |

| U    | 12.0        | 0.472        |

| W    | 0.75±0.2    | 0.030+0.008  |

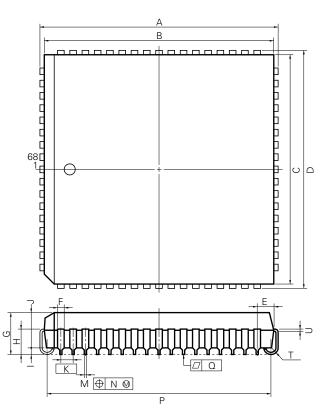

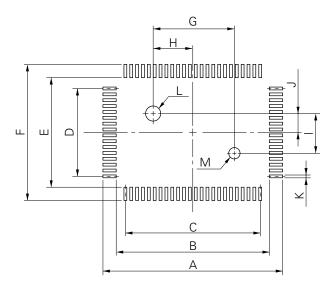

## **74 PIN CERAMIC WQFN**

### NOTE

Each lead centerline is located within 0.10 mm (0.004 inch) of its true position (T.P.) at maximum material condition.

X74KW-100A-1

| ITEM | MILLIMETERS | INCHES                                    |  |  |

|------|-------------|-------------------------------------------|--|--|

| Α    | 20.0±0.4    | 0.787 <sup>+0.017</sup> <sub>-0.016</sub> |  |  |

| В    | 18.0        | 0.709                                     |  |  |

| С    | 18.0        | 0.709                                     |  |  |

| D    | 20.0±0.4    | 0.787 <sup>+0.017</sup> <sub>-0.016</sub> |  |  |

| Е    | 1.94        | 0.076                                     |  |  |

| F    | 2.14        | 0.084                                     |  |  |

| G    | 4.0 MAX.    | 0.158 MAX.                                |  |  |

| Н    | 0.51±0.10   | 0.020±0.004                               |  |  |

| I    | 0.10        | 0.004                                     |  |  |

| J    | 1.0 (T.P.)  | 0.039 (T.P.)                              |  |  |

| K    | 1.0±0.2     | $0.039^{+0.009}_{-0.008}$                 |  |  |

| Q    | C 0.3       | C 0.012                                   |  |  |

| R    | 2.0         | 0.079                                     |  |  |

| S    | 2.0         | 0.079                                     |  |  |

| Т    | R 2.0       | R 0.079                                   |  |  |

| U    | 10.0        | 0.394                                     |  |  |

| W    | 0.7±0.2     | 0.028+0.008                               |  |  |

| Υ    | C 1.5       | C 0.059                                   |  |  |

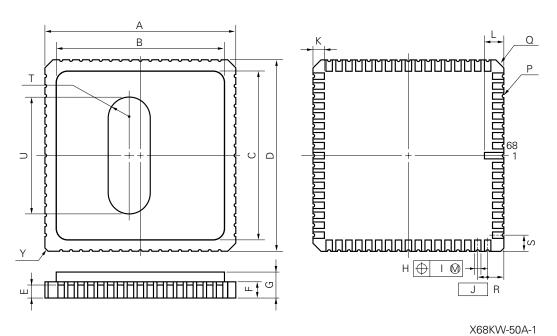

## **68 PIN CERAMIC WQFN**

### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

### X68KW-50A-1

| ITEM | MILLIMETERS | INCHES                    |  |  |

|------|-------------|---------------------------|--|--|

| А    | 24.13±0.4   | 0.950±0.016               |  |  |

| В    | 21.5        | 0.846                     |  |  |

| С    | 21.5        | 0.846                     |  |  |

| D    | 24.13±0.4   | 0.950±0.016               |  |  |

| Е    | 1.65        | 0.065                     |  |  |

| F    | 2.03        | 0.080                     |  |  |

| G    | 3.50 MAX.   | 0.138 MAX.                |  |  |

| Н    | 0.64±0.10   | $0.025^{+0.005}_{-0.004}$ |  |  |

| I    | 0.12        | 0.005                     |  |  |

| J    | 1.27 (T.P.) | 0.05 (T.P.)               |  |  |

| K    | 1.27±0.2    | 0.05±0.008                |  |  |

| L    | 2.16±0.2    | 0.085±0.008               |  |  |

| Р    | R 0.2       | R 0.008                   |  |  |

| Q    | C 1.02      | C 0.04                    |  |  |

| R    | 1.905       | 0.075                     |  |  |

| S    | 1.905       | 0.075                     |  |  |

| Т    | R 3.0       | R 0.118                   |  |  |

| U    | 12.0        | 0.472                     |  |  |

| Υ    | C 0.5       | C 0.020                   |  |  |

#### 9. RECOMMENDED SOLDERING CONDITIONS

It is recommended that this device be soldered under the following conditions.

For details on the recommended soldering conditions, refer to information document "Semiconductor Devices Mounting Technology Manual" (IEI-1207).

For soldering methods and conditions other than those recommended, please contact your NEC sales representative.

Table 9-1. Soldering Conditions for Surface Mount Devices (1/2)

## $\mu$ PD78P322GF-3B9: 80-pin plastic QFP (14 $\times$ 20 mm)

| Soldering Method                                         | Soldering Conditions                                                    | Recommended Soldering |

|----------------------------------------------------------|-------------------------------------------------------------------------|-----------------------|

|                                                          |                                                                         | Code                  |

| Infrared reflow                                          | Package peak temperature: 235°C,                                        | IR35-207-2            |

|                                                          | Time: 30 seconds max. (210°C min.),                                     |                       |